Why Attend

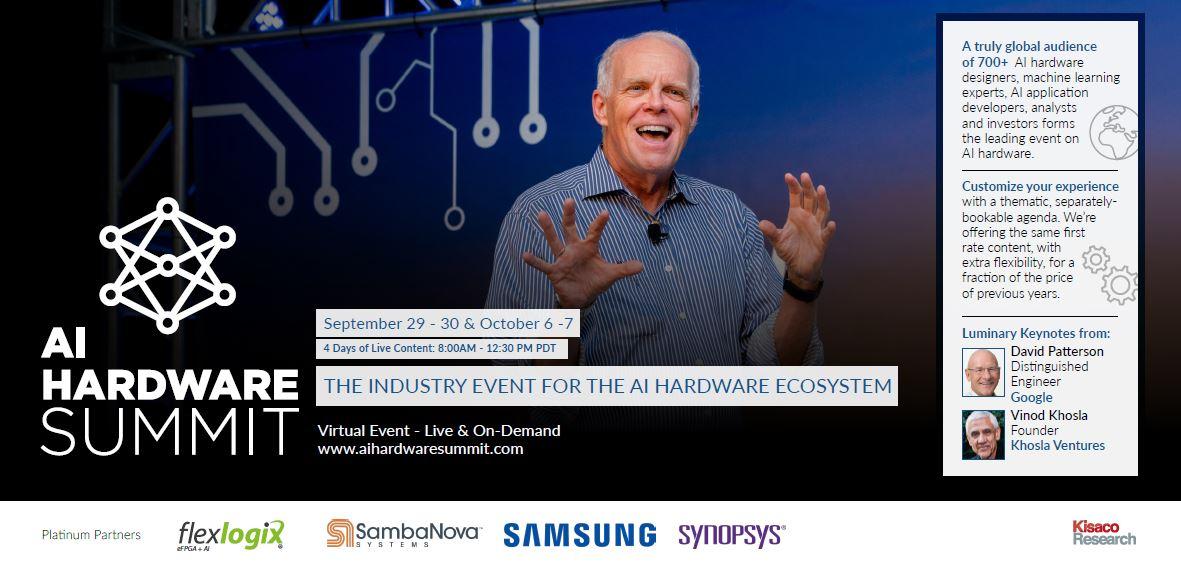

- Luminary Keynotes: Unique perspectives from industry luminaries such as Turing Award Winner David Patterson, and venture capital pathfinder and computer hardware industry veteran, Vinod Khosla. Returning 2019 AIHW Summit luminary Lip-Bu Tan, CEO of Cadence Design Systems.

- Innovations and Optimizations of Silicon & Systems for AI Training & Inference: Product launches & deep-dives from C-level executives in the AI Hardware industry.

- Optimizing Machine Learning Systems: Hyperscaler perspectives on designing & engineering bleeding-edge AI systems, from hardware through software. ML system co-design and protecting compute performance gains by eliminating system-level inefficiencies.

- Inference in Client (Edge) Computing: Applications for AI accelerators in cameras, consumer electronics, autonomous vehicles etc.

- Preserving Developer Efficiency in the Adoption of Novel AI Hardware

- Beyond Compute: AI’s Impact on memory, storage & networking: Innovations in HBM, on-chip memory and NVM, I/O bottlenecks, data transfer & high-speed interconnects.

- Managing Machine Learning Models at Scale: Machine Learning hardware robustness & reprogrammability, model standardization & interoperability.

- Financial & Industrial Analysis: New in 2020: Presentation of the results and insights from AI Hardware Summit’s first comprehensive vendor comparison report, detailing 20 vendors. VC investment and broader market trends & dynamics, benchmarking & metrics.

Networking at the virtual AI Hardware Summit

Get access to the attendee list before the show and schedule 1-2-1 meetings with attendees, speakers and sponsors throughout the conference so you don’t miss out on networking & interaction opportunities.

Advisory Board

Andrew Feldman

Andrew Feldman is co-founder and CEO of Cerebras Systems. He is an entrepreneur dedicated to pushing boundaries in the compute space. Prior to Cerebras, he co-founded and was CEO of SeaMicro, a pioneer of energy-efficient, high-bandwidth microservers. SeaMicro was acquired by AMD in 2012 for $357M. Before SeaMicro, Andrew was the Vice President of Product Management, Marketing and BD at Force10 Networks which was later sold to Dell Computing for $800M. Prior to Force10 Networks, Andrew was the Vice President of Marketing and Corporate Development at RiverStone Networks from the company’s inception through IPO in 2001. Andrew holds a BA and an MBA from Stanford University.

Lip-Bu Tan

Lip-Bu Tan is Founder and Chairman of Walden International (“WI”), and Founding Managing Partner of Celesta Capital and Walden Catalyst Ventures, with over $5 billion under management. He formerly served as Chief Executive Officer and Executive Chairman of Cadence Design Systems, Inc. He currently serves on the Board of Schneider Electric SE (SU: FP), Intel Corporation (NASDAQ: INTC), and Credo Semiconductor (NASDAQ: CRDO).

Lip-Bu focuses on semiconductor/components, cloud/edge infrastructure, data management and security, and AI/machine learning.Lip-Bu received his B.S. from Nanyang University in Singapore, his M.S. in Nuclear Engineering from the Massachusetts Institute of Technology, and his MBA from the University of San Francisco. He also received his honorary degree for Doctor of Humane Letters from the University of San Francisco. Lip-Bu currently serves on Carnegie Mellon University (CMU)’s Board of Trustees and the School of Engineering Dean’s Council, Massachusetts Institute of Technology (MIT)’s School of Engineering Dean’s Advisory Council, University of California Berkeley (UCB)’s College of Engineering Advisory Board and their Computing, Data Science, and Society Advisory Board, and University of California San Francisco (UCSF)’s Executive Council. He’s also a member of the Global Advisory Board of METI Japan, The Business Council, and Committee 100. He also served on the board of the Board of Global Semiconductor Alliance (GSA) from 2009 to 2021, and as a Trustee of Nanyang Technological University (NTU) in Singapore from 2006 to 2011. Lip-Bu has been named one of the Top 10 Venture Capitalists in China by Zero2ipo and was listed as one of the Top 50 Venture Capitalists on the Forbes Midas List. He’s the recipient of imec’s 2023 Lifetime of Innovation Award, the Semiconductor Industry Association (SIA) 2022 Robert N. Noyce Award, and GSA’s 2016 Dr. Morris Chang's Exemplary Leadership Award. In 2017, he was ranked #1 of the most well-connected executives in the technology industry by the analytics firm Relationship Science.

Rashmi Gopinath

Rashmi Gopinath is a General Partner at B Capital Group where she leads the fund’s enterprise software practice in cloud infrastructure, cybersecurity, devops, and AI/ML sectors. She brings over two decades of experience investing and operating in cutting-edge enterprise technologies. She led B Capital’s investments in over 24 companies such as DataRobot, FalconX, Clari, Phenom People, Synack, Innovaccer, Labelbox, Fabric, 6Sense, Highspot, Pendo, Starburst, OwnBackup, Figment, Perimeter81, Zesty, among others.

Rashmi was previously a Managing Director at M12, Microsoft’s venture fund, where she led investments globally in enterprise software and sat on several boards including Synack, Innovaccer, Contrast Security, Frame, UnravelData, Incorta, among others.

Prior to M12, Rashmi was an Investment Director with Intel Capital where she was involved in the firm’s investments in startups including MongoDB (Nasdaq: MDB), ForeScout (Nasdaq: FSCT), Maginatics (acq. by EMC), BlueData (acq. by HPE), among others. Rashmi held operating roles at high-growth startups such as BlueData (acq. by HPE) and Couchbase (Nasdaq: BASE) where she led global business development, product and marketing roles. She began her career in engineering and product roles at Oracle and GE Healthcare. She earned an M.B.A. from Northwestern University, and a B.S. in Electrical Engineering from University of Mumbai in India.

Karl Freund

Karl Freund is the founder and principal analyst of Cambrian AI Research. Prior to this, he was Moor Insights & Strategy’s consulting lead for HPC and Deep Learning. His recent experiences as the VP of Marketing at AMD and Calxeda, as well as his previous positions at Cray and IBM, positions him as a leading industry expert in these rapidly evolving industries. Karl works with investment and technology customers to help them understand the emerging Deep Learning opportunity in data centers, from competitive landscape to ecosystem to strategy.

Karl has worked directly with datacenter end users, OEMs, ODMs and the industry ecosystem, enabling him to help his clients define the appropriate business, product, and go-to-market strategies. He is also recognized expert on the subject of low-power servers and the emergence of ARM in the datacenter and has been a featured speaker at scores of investment and industry conferences on this topic.

Accomplishments during his career include:

- Led the revived HPC initiative at AMD, targeting APUs at deep learning and other HPC workloads

- Created an industry-wide thought leadership position for Calxeda in the ARM Server market

- Helped forge the early relationship between HP and Calxeda leading to the surprise announcement of HP Moonshot with Calxeda in 2011

- Built the IBM Power Server brand from 14% market share to over 50% share

- Integrated the Tivoli brand into the IBM company’s branding and marketing organization

- Co-Led the integration of HP and Apollo Marketing after the Boston-based desktop company’s acquisition

Karl’s background includes RISC and Mainframe servers, as well as HPC (Supercomputing). He has extensive experience as a global marketing executive at IBM where he was VP Marketing (2000-2010), Cray where he was VP Marketing (1995-1998), and HP where he was a Division Marketing Manager (1979-1995).

Yvonne Lutsch

Yvonne is an accomplished Investment Principal at Bosch Ventures affiliate office located in Sunnyvale, and sources, evaluates, and executes venture capital deals in North America. Her specialty are investments in deep tech fields such as AI, edge and next gen. computing incl. quantum, robotics, industrial IoT, mobility, climate tech, semiconductors, or sensors. She is an investor and non-executive board member of Bosch Ventures’ portfolio companies Syntiant, Zapata AI, UltraSense Systems, Aclima, and Recogni.

Prior to this position Yvonne was Director of Technology Scouting and Business Development, building up an Innovation Hub in Silicon Valley including startup scouting, business development while advising executives of the Bosch business units on their strategy. She has more than two decades of solid experience in manufacturing operations and engineering in the automotive and consumer electronics space – gained through different executive roles at Bosch in Germany.

Yvonne received a diploma in Experimental Physics from University of Siegen, Germany, and holds a PhD in Applied Physics from University of Tuebingen, Germany.

Kunle Olukotun

Kunle Olukotun is Cadence Design Professor of Electrical Engineering and Computer Science at Stanford University. He founded Afara Websystems, acquired by Sun in 2002. He is a Pioneer of Chip Multiprocessor Designs, Director of the Stanford Pervasive Parallelism Lab, and Co-leader of the Data Analytics for What’s Next (DAWN) research program.

In 2017 Olukotun and Chris Ré founded SambaNova Systems. SambaNova Systems has developed a disruptive next-generation computing platform to power machine learning and data analytics.

Cliff Young

Marc Tremblay

Marc Tremblay, Ph.D.: Marc is a Distinguished Engineer and VP in the Office of the CTO (OCTO) at Microsoft. His current role is to drive the strategic and technical direction of the company on silicon and hardware systems from a cross-divisional standpoint. This includes Artificial Intelligence, from supercomputer to client devices to Xbox, etc., and general-purpose computing. Throughout his career, Marc has demonstrated a passion for translating high-level application requirements into optimizations up and down the stack, all the way to silicon. AI has been his focus for the past several years, but his interests also encompass accelerators for the cloud, scale-out systems, and process technology. He has given multiple keynotes on AI Hardware, published many papers on throughput computing, multi-cores, multithreading, transactional memory, speculative multi-threading, Java computing, etc. and he is an inventor of over 300 patents on those topics.

Prior to Microsoft, Marc was the CTO of Microelectronics at Sun Microsystems. As a Sun Fellow and SVP, he was responsible for the technical leadership of 1200 engineers. Throughout his career, he has started, architected, led, defined and shipped a variety of microprocessors such as superscalar RISC processors (UltraSPARC I/II), bytecode engines (picoJava), VLIW, media and Java-focused (MAJC), and the first processor to implement speculative multithreading and transactional memory (ROCK – first silicon). He received his M.S. and Ph.D. degrees in Computer Sciences from UCLA and his Physics Engineering degree from Laval University in Canada. Marc is on the board of directors of QuantalRF.

Victoria Rege

Victoria has over a decade of experience in the semiconductor space. She currently heads up Strategic Partnerships at Graphcore, working with key customers and leading Research & Universities AI engagements. Previously she held several leadership positions at NVIDIA from global alliances, product marketing and campaigns to the founding of the GPU Technology Conference. Prior to joining NVIDIA, Victoria worked in the hedge fund space, as Executive Director for the Hedge Fund Business Operations Association. Victoria is a frequent contributor to ACM SIGGRAPH and is Immersive Chair for the SIGGRAPH 2019 Conference. She's also an active member of the Consumer Technology Association's AI Working Group.

Cheng Wang

Originally from Shanghai, PRC. Cheng has led the architecture, silicon implementation and software development for eFPGA over multiple generations from 180nm-16nm and now AI inferencing development at Flex Logix. Two years as VLSI designer at Zoran. BSEECS, UC Berkeley. MSEE, EE PhD UCLA: designed 5 FPGA chips from 90nm to 40nm. 2013 Distinguished PhD Dissertation Award. 2014 ISSCC Lewis Winner Award for Outstanding Paper. Multiple patents at UCLA and Flex Logix.

Rick Merritt

Jimmy Pike

Jimmy D. Pike is a Senior Vice President and Senior Fellow at Dell EMC and serves as a senior system architect and technologist in the office of Dell’s Server and Infrastructure System’s CTO. In addition to his duties as an “at large” technologist, he focuses on high-performance computing, machine learning, and edge computing.

A longtime industry figure with more than 50 patents, Jimmy has served in various executive and technology roles:

• An analyst at the analyst firm of Moor Insights & Strategy

• Chief Architect of Dell’s Enterprise Solutions group and HPC lead technologist

• Chief Architect and Technologist for Dell’s Data Center group.

Jimmy has as also served in various other leadership roles at Intel, AT&T, NCR, and Harris Corporation.

Sailesh Kottapalli

Sailesh Kottapalli is an Intel Senior Fellow and the chief architect of data center processor architecture in the Silicon Engineering Group. He leads a team of architects responsible for developing the architecture of Intel® Xeon® and Intel® Atom™ server product lines as well as the overall compute solutions strategy for datacenter segment. He also leads a cross-organizations effort in driving the technology leadership on the Interconnect pillar. Kottapalli joined Intel in 1996 as a design engineer working on the first Intel® Itanium® processor, then code-named “Merced.” Subsequently, he served as lead engineer for several Intel Itanium and Intel Xeon processor evaluations, and more recently, as lead architect for a series of Intel Xeon server processors. His work in this area earned Kottapalli an Intel Achievement Award for delivering record generational performance improvements in a high-end server product. An active participant in industry and internal conferences, Kottapalli has authored or co-authored several published technical papers, delivered talks and taken part in roundtables and panel discussions. He has also been granted approximately three dozen patents in processor architecture, with additional patents pending. Kottapalli holds a bachelor’s degree in computer science from Andhra University in India and a master’s degree in computer engineering from Virginia Tech.

Speakers

David Patterson

David Patterson is a UC Berkeley professor of the graduate school, a Google distinguished engineer, and the RISC-V Foundation Vice-Chair. He received his BA, MS, and PhD degrees from UCLA. His Reduced Instruction Set Computer (RISC), Redundant Array of Inexpensive Disks (RAID), and Network of Workstation projects helped lead to multibillion-dollar industries. This work led to about 40 awards for research, teaching, and service plus many papers and seven books. The best known book is Computer Architecture: A Quantitative Approach and the newest is The RISC-V Reader. He and his co-author John Hennessy shared the 2017 ACM A.M Turing Award.

Vinod Khosla

Vinod Khosla is an entrepreneur, investor, and technology fan. He is the founder of Khosla Ventures, focused on impactful technology investments in software, AI, robotics, 3D printing, healthcare and more. Mr. Khosla was a co-founder of Daisy systems and founding CEO of Sun Microsystems where he pioneered open systems and commercial RISC processors. One of Mr. Khosla’s greatest passions is being a mentor to entrepreneurs, assisting entrepreneurs and helping them build technology-based businesses. Mr. Khosla is driven by the desire to make positive impact through using to technology to reinvent societal infrastructure and multiply resources. He is also passionate about Social Entrepreneurship. Vinod holds a Bachelor of Technology in Electrical Engineering from IIT, New Delhi, a Master's in Biomedical Engineering from Carnegie Mellon University and an MBA from the Stanford Graduate School of Business.

Rashmi Gopinath

Rashmi Gopinath is a General Partner at B Capital Group where she leads the fund’s enterprise software practice in cloud infrastructure, cybersecurity, devops, and AI/ML sectors. She brings over two decades of experience investing and operating in cutting-edge enterprise technologies. She led B Capital’s investments in over 24 companies such as DataRobot, FalconX, Clari, Phenom People, Synack, Innovaccer, Labelbox, Fabric, 6Sense, Highspot, Pendo, Starburst, OwnBackup, Figment, Perimeter81, Zesty, among others.

Rashmi was previously a Managing Director at M12, Microsoft’s venture fund, where she led investments globally in enterprise software and sat on several boards including Synack, Innovaccer, Contrast Security, Frame, UnravelData, Incorta, among others.

Prior to M12, Rashmi was an Investment Director with Intel Capital where she was involved in the firm’s investments in startups including MongoDB (Nasdaq: MDB), ForeScout (Nasdaq: FSCT), Maginatics (acq. by EMC), BlueData (acq. by HPE), among others. Rashmi held operating roles at high-growth startups such as BlueData (acq. by HPE) and Couchbase (Nasdaq: BASE) where she led global business development, product and marketing roles. She began her career in engineering and product roles at Oracle and GE Healthcare. She earned an M.B.A. from Northwestern University, and a B.S. in Electrical Engineering from University of Mumbai in India.

Andrew Feldman

Andrew Feldman is co-founder and CEO of Cerebras Systems. He is an entrepreneur dedicated to pushing boundaries in the compute space. Prior to Cerebras, he co-founded and was CEO of SeaMicro, a pioneer of energy-efficient, high-bandwidth microservers. SeaMicro was acquired by AMD in 2012 for $357M. Before SeaMicro, Andrew was the Vice President of Product Management, Marketing and BD at Force10 Networks which was later sold to Dell Computing for $800M. Prior to Force10 Networks, Andrew was the Vice President of Marketing and Corporate Development at RiverStone Networks from the company’s inception through IPO in 2001. Andrew holds a BA and an MBA from Stanford University.

Lip-Bu Tan

Lip-Bu Tan is Founder and Chairman of Walden International (“WI”), and Founding Managing Partner of Celesta Capital and Walden Catalyst Ventures, with over $5 billion under management. He formerly served as Chief Executive Officer and Executive Chairman of Cadence Design Systems, Inc. He currently serves on the Board of Schneider Electric SE (SU: FP), Intel Corporation (NASDAQ: INTC), and Credo Semiconductor (NASDAQ: CRDO).

Lip-Bu focuses on semiconductor/components, cloud/edge infrastructure, data management and security, and AI/machine learning.Lip-Bu received his B.S. from Nanyang University in Singapore, his M.S. in Nuclear Engineering from the Massachusetts Institute of Technology, and his MBA from the University of San Francisco. He also received his honorary degree for Doctor of Humane Letters from the University of San Francisco. Lip-Bu currently serves on Carnegie Mellon University (CMU)’s Board of Trustees and the School of Engineering Dean’s Council, Massachusetts Institute of Technology (MIT)’s School of Engineering Dean’s Advisory Council, University of California Berkeley (UCB)’s College of Engineering Advisory Board and their Computing, Data Science, and Society Advisory Board, and University of California San Francisco (UCSF)’s Executive Council. He’s also a member of the Global Advisory Board of METI Japan, The Business Council, and Committee 100. He also served on the board of the Board of Global Semiconductor Alliance (GSA) from 2009 to 2021, and as a Trustee of Nanyang Technological University (NTU) in Singapore from 2006 to 2011. Lip-Bu has been named one of the Top 10 Venture Capitalists in China by Zero2ipo and was listed as one of the Top 50 Venture Capitalists on the Forbes Midas List. He’s the recipient of imec’s 2023 Lifetime of Innovation Award, the Semiconductor Industry Association (SIA) 2022 Robert N. Noyce Award, and GSA’s 2016 Dr. Morris Chang's Exemplary Leadership Award. In 2017, he was ranked #1 of the most well-connected executives in the technology industry by the analytics firm Relationship Science.

Rene Haas

Rene Haas is the president of Arm’s IP Products Group (IPG) and a member of the Arm Executive Committee. Rene took over management of IPG in January 2017 and is responsible for all IPG activities including product development, engineering, sales, marketing, and commercial operations.

Rene was previously Arm’s chief commercial officer in charge of global sales and marketing, a position he held since October 2015. Prior to that he served as the vice president of strategic alliances.

Before joining Arm, Rene held several applications management, applications engineering and product engineering roles, including seven years at NVIDIA as vice president and general manager of its computing products business.

Rene is based in Cambridge, UK, but spends significant time in the major technology centers in the US and Asia Pacific.

Carole-Jean Wu

Carole-Jean Wu is a Research Scientist at Facebook AI Research. Her research focuses on designing systems for at-scale execution of machine learning, such as personalized recommender systems and for mobile deployment. More generally, her research interests are in computer architecture with particular focus on energy- and memory-efficient systems. Carole-Jean chairs MLPerf Recommendation Benchmark Advisory Board and co-chairs MLPerf Inference. She received her M.A. and Ph.D. from Princeton and B.Sc. from Cornell. She holds tenure from ASU and is the recipient of the NSF CAREER Award, Facebook AI Infrastructure Mentorship Award, the IEEE Young Engineer of the Year Award, the Science Foundation Arizona Bisgrove Early Career Scholarship, and the Intel PhD Fellowship, among a number of Best Paper awards.

Cheng Wang

Originally from Shanghai, PRC. Cheng has led the architecture, silicon implementation and software development for eFPGA over multiple generations from 180nm-16nm and now AI inferencing development at Flex Logix. Two years as VLSI designer at Zoran. BSEECS, UC Berkeley. MSEE, EE PhD UCLA: designed 5 FPGA chips from 90nm to 40nm. 2013 Distinguished PhD Dissertation Award. 2014 ISSCC Lewis Winner Award for Outstanding Paper. Multiple patents at UCLA and Flex Logix.

Gayathri Radhakrishnan

Gayathri is currently Partner at Hitachi Ventures. Prior to that, she was with Micron Ventures, actively investing in startups that apply AI to solve critical problems in the areas of Manufacturing, Healthcare and Automotive. She brings over 20 years of multi-disciplinary experience across product management, product marketing, corporate strategy, M&A and venture investments in large Fortune 500 companies such as Dell and Corning and in startups. She has also worked as an early stage investor at Earlybird Venture Capital, a premier European venture capital fund based in Germany. She has a Masters in EE from The Ohio State University and MBA from INSEAD in France. She is also a Kauffman Fellow - Class 16.

Karl Freund

Karl Freund is the founder and principal analyst of Cambrian AI Research. Prior to this, he was Moor Insights & Strategy’s consulting lead for HPC and Deep Learning. His recent experiences as the VP of Marketing at AMD and Calxeda, as well as his previous positions at Cray and IBM, positions him as a leading industry expert in these rapidly evolving industries. Karl works with investment and technology customers to help them understand the emerging Deep Learning opportunity in data centers, from competitive landscape to ecosystem to strategy.

Karl has worked directly with datacenter end users, OEMs, ODMs and the industry ecosystem, enabling him to help his clients define the appropriate business, product, and go-to-market strategies. He is also recognized expert on the subject of low-power servers and the emergence of ARM in the datacenter and has been a featured speaker at scores of investment and industry conferences on this topic.

Accomplishments during his career include:

- Led the revived HPC initiative at AMD, targeting APUs at deep learning and other HPC workloads

- Created an industry-wide thought leadership position for Calxeda in the ARM Server market

- Helped forge the early relationship between HP and Calxeda leading to the surprise announcement of HP Moonshot with Calxeda in 2011

- Built the IBM Power Server brand from 14% market share to over 50% share

- Integrated the Tivoli brand into the IBM company’s branding and marketing organization

- Co-Led the integration of HP and Apollo Marketing after the Boston-based desktop company’s acquisition

Karl’s background includes RISC and Mainframe servers, as well as HPC (Supercomputing). He has extensive experience as a global marketing executive at IBM where he was VP Marketing (2000-2010), Cray where he was VP Marketing (1995-1998), and HP where he was a Division Marketing Manager (1979-1995).

Kunle Olukotun

Kunle Olukotun is Cadence Design Professor of Electrical Engineering and Computer Science at Stanford University. He founded Afara Websystems, acquired by Sun in 2002. He is a Pioneer of Chip Multiprocessor Designs, Director of the Stanford Pervasive Parallelism Lab, and Co-leader of the Data Analytics for What’s Next (DAWN) research program.

In 2017 Olukotun and Chris Ré founded SambaNova Systems. SambaNova Systems has developed a disruptive next-generation computing platform to power machine learning and data analytics.

Yvonne Lutsch

Yvonne is an accomplished Investment Principal at Bosch Ventures affiliate office located in Sunnyvale, and sources, evaluates, and executes venture capital deals in North America. Her specialty are investments in deep tech fields such as AI, edge and next gen. computing incl. quantum, robotics, industrial IoT, mobility, climate tech, semiconductors, or sensors. She is an investor and non-executive board member of Bosch Ventures’ portfolio companies Syntiant, Zapata AI, UltraSense Systems, Aclima, and Recogni.

Prior to this position Yvonne was Director of Technology Scouting and Business Development, building up an Innovation Hub in Silicon Valley including startup scouting, business development while advising executives of the Bosch business units on their strategy. She has more than two decades of solid experience in manufacturing operations and engineering in the automotive and consumer electronics space – gained through different executive roles at Bosch in Germany.

Yvonne received a diploma in Experimental Physics from University of Siegen, Germany, and holds a PhD in Applied Physics from University of Tuebingen, Germany.

Julien Simon

As the Global AI & Machine Learning Evangelist, Julien focuses on helping developers and enterprises bring their ideas to life. He frequently speaks at conferences, blogs on the AWS Blog and Medium, and runs an AI/ML podcast.

Prior to joining AWS, Julien served for 10 years as CTO/VP Engineering in top-tier web startups where he led large Software and Ops teams in charge of thousands of servers worldwide. In the process, he fought his way through a wide range of technical, business and procurement issues, which helped him gain a deep understanding of physical infrastructure, its limitations and how cloud computing can help.

Last but not least, Julien holds ten AWS certifications.

David Kanter

David founded and leads MLCommons, to make machine learning better for everyone through benchmarks, such as MLPerf, and building datasets and tools for data-centric AI.

The mission of MLCommons™ is to make machine learning better for everyone. Together with its 50+ founding Members and Affiliates, including startups, leading companies, academics, and non-profits from around the globe, MLCommons will help grow machine learning from a research field into a mature industry through benchmarks, public datasets and best practices. MLCommons firmly believes in the power of open-source and open data. Our software projects are generally available under the Apache 2.0 license and our datasets generally use CC-BY 4.0.

Peter Mattson

Peter Mattson leads the ML Performance Measurement at Google. He co-founded and is the General Chair of MLPerf. Previously, he founded the Programming Systems and Applications Group at NVIDIA Research, was VP of software infrastructure for Stream Processors Inc (SPI), and was a managing engineer at Reservoir Labs. His research focuses on accelerating and understanding the behavior of machine learning systems by applying novel benchmarks and analysis tools. Peter holds a PhD and MS from Stanford University and a BS from the University of Washington.

Greg Diamos

Greg leads transformation engineering at Landing AI, focusing on building new AI engineering organizations. He is a founding member of MLPerf. Previously he lead AI research at Baidu’s Silicon Valley AI Lab (SVAIL), where he helped develop the Deep Speech and Deep Voice systems. Before Baidu, Greg contributed to the design of compiler and microarchitecture technologies used in the Volta GPU at NVIDIA, including the invention of the SIMT independent thread scheduling system. Greg holds a PhD from the Georgia Institute of Technology, where he led the development of the GPU-Ocelot dynamic compiler, which targeted CPUs and GPUs from the same program representation.

Dileep George

Before cofounding Vicarious, Dileep was CTO of Numenta, an AI company he cofounded with Jeff Hawkins and Donna Dubinsky. Before Numenta, Dileep was a Research Fellow at the Redwood Neuroscience Institute. Dileep has authored 22 patents and several influential papers on the mathematics of brain circuits. Dileep’s research on hierarchical models of the brain earned him a PhD in Electrical Engineerings from Stanford University. He earned in MS in EE from Stanford and his BS from IIT in Bombay.

Zaid Kahn

Zaid is currently GM in Cloud Hardware Infrastructure Engineering where he leads a team focusing on advanced architecture and engineering efforts for AI. He is passionate about building balanced teams of artists and soldiers that solve incredibly difficult problems at scale.

Prior to Microsoft Zaid was head of infrastructure engineering at LinkedIn responsible for all aspects of engineering for Datacenters, Compute, Networking, Storage and Hardware. He also lead several software development teams spanning from BMC, network operating systems, server and network fleet automation to SDN efforts inside the datacenter and global backbone including edge. He introduced the concept of disaggregation inside LinkedIn and pioneered JDM with multiple vendors through key initiatives like OpenSwitch, Open19 essentially controlling destiny for hardware development at LinkedIn. During his 9 year tenure at LinkedIn his team scaled network and systems 150X, members from 50M to 675M, and hiring someone every 7 seconds on the LinkedIn Platform.

Prior to LinkedIn Zaid was Network Architect at WebEx responsible for building the MediaTone network and later I built a startup that built a pattern recognition security chip using NPU/FPGA. Zaid holds several patents in networking and SDN and is also a recognized industry leader. He previously served as a board member of the Open19 Foundation and San Francisco chapter of Internet Society. Currently he serves on DE-CIX and Pensando advisory boards.

Michael Azoff

With over 17 years analyst experience, most recently at Ovum/ Informa, Michael Azoff joined Kisaco Research, the company behind the AI Hardware and Edge AI Summit series, in 2020 as Chief Analyst.

Eitan Michael Azoff, PhD, MSc, BEng.

HQ’d in Kisaco Research’s London office, Michael's current focus is launching Kisaco Research vendor product comparison reports with the new Kisaco Leadership Chart (KLC) analyst chart. The first KLC is also the first analyst chart in the AI chip industry, with 16 vendors having participated in the research.

In his career Michael worked at Rutherford Appleton Laboratory building simulators for electron and hole transport in semiconductors for UK national and European community research projects and published papers in learned journals. He then turned to building neural networks and created a startup selling his Prognostica Microsoft Excel add-in for time series forecasting, and wrote a book on the topic for publisher John Wiley & Sons in 1994.

Since 2003 Michael has worked as an IT industry analyst covering software engineering topics, from agile and DevOps, to application lifecycle management and cloud native computing. He started covering machine learning when deep learning emerged as the most recent wave of interest in AI and left his position as Distinguished Analyst at Ovum/Informa to join Kisaco Research and help build an analyst capability within the company.

My analyst coverage areas at KR Analysis

My first research project at KR was to create the first analyst comparison chart for AI chips. We invited AI chip producers to participate and were fortunate to have 16 vendors participate from across the globe: USA, UK, France, and China, and a mix of established players (Nvidia, Imagination, Intel, and Xilinx, to startups.

Our analysis showed that the market naturally fell into three areas of hot activity:

▪ Data centers and high-performance computing environments (HPC): here large boxes are installed and the aim is to achieve maximum performance for training and inferencing AI systems. The buyers are cloud hyperscalars, national research labs and agencies, and some large enterprises with big investments in AI.

▪ Small edge: the opposite end of the spectrum, building the smallest useful chip possible to sell as cheap as possible and embed in edge devices. AI is inferencing here.

▪ Automotive: an active industry in AI but highly regulated creating hurdles and technology adoption cadences that can be challenging for suppliers. AI is mainly inferencing here (for systems installed in vehicles).

We produced four Kisaco Leadership Charts out of this research.

We are also researching the machine learning (ML) software tools space, and our first report here is ML Lifecycle Solutions. The biggest challenge for enterprises is taking the research AI systems developed by their data scientist and deploying these into production at scale. Using a host of open source tools to achieve this is possible but time consuming to build and maintain, as well as prone to breakdown. This is why the ML lifecycle solution space exists.

Finally, in our first batch of KR Analysis reports we produced the KLC on engineering application lifecycle management (ALM) solutions. While ALM has been in existence as a distinct practice since KR Analysis and Michael Azoff introduction © Kisaco Research. All rights reserved. Unauthorized reproduction prohibited. 4 around 2003, it continues to evolve. We found the engineering and highly regulated industries relying on engineering and compliance oriented ALM to help manage risk and complexity.

Bryan Catanzaro

Bryan Catanzaro is vice president of Applied Deep Learning Research at NVIDIA, where he leads a team finding new ways to use AI to improve projects ranging from language understanding to computer graphics and chip design. Bryan's research at NVIDIA led to the creation of CUDNN, and more recently, he helped lead the team that invented DLSS 2.0. Prior to NVIDIA, he worked at Baidu to create next-generation systems for training and deploying end-to-end, deep learning-based speech recognition. Bryan received his PhD in Electrical Engineering and Computer Sciences from the University of California, Berkeley.

Vivenne Sze

Priyanka Raina

Shahin Farshschi

Shahin empowers entrepreneurs aiming to accelerate humanity towards a brighter future through feats of engineering. He is passionate about artificial intelligence, robots, space, cars, and engines—pretty much anything you might find in an episode of Star Trek.

He led Lux’s investments in Silicon Clocks (NASDAQ:SLAB), which shrank electronics by baking bulky quartz crystals into silicon chips; SiBeam (NASDAQ:SIMG), which aims to eliminate wires from living rooms by introducing full-HD wireless connectivity; Planet, which is launching the world’s largest fleet of Earth-imaging satellites; Plethora, which is rolling out a fleet of robotic machine shops; Flex Logix, making chips that can reprogram themselves; Nervana (NASDAQ:INTC), the first full-stack platform for machine intelligence; Mythic, bringing powerful AI to miniature, inexpensive devices; Astranis, which is building low-cost telecommunications satellites; Embodied Intelligence, which empowers industrials to perceive and act like humans; Aeva, a new sensing paradigm for autonomous machines; Arraiy, a platform for automating visual effects; SubSpace, a company providing real-time, latency-free internet; and Scaled Inference.

Previously, Shahin co-founded Vista Integrated Systems, which built wireless vital sign monitors based on a neural interface technology he developed during his PhD at UCLA. Shahin also developed hybrid electric vehicles for GM in Detroit, worked as a software developer in several Silicon Valley startups, and researched new techniques for semiconductor manufacturing. He earned his Bachelor’s in EECS at UC Berkeley.

Tatiana Shpeisman

Steven Woo

I was drawn to Rambus to focus on cutting edge computing technologies. Throughout my 15+ year career, I’ve helped invent, create and develop means of driving and extending performance in both hardware and software solutions. At Rambus, we are solving challenges that are completely new to the industry and occur as a response to deployments that are highly sophisticated and advanced.

As an inventor, I find myself approaching a challenge like a room filled with 100,000 pieces of a puzzle where it is my job to figure out how they all go together – without knowing what it is supposed to look like in the end. For me, the job of finishing the puzzle is as enjoyable as the actual process of coming up with a new, innovative solution.

For example, RDRAM®, our first mainstream memory architecture, implemented in hundreds of millions of consumer, computing and networking products from leading electronics companies including Cisco, Dell, Hitachi, HP, Intel, etc. We did a lot of novel things that required inventiveness – we pushed the envelope and created state of the art performance without making actual changes to the infrastructure.

I’m excited about the new opportunities as computing is becoming more and more pervasive in our everyday lives. With a world full of data, my job and my fellow inventors’ job will be to stay curious, maintain an inquisitive approach and create solutions that are technologically superior and that seamlessly intertwine with our daily lives.

After an inspiring work day at Rambus, I enjoy spending time with my family, being outdoors, swimming, and reading.

Education

- Ph.D., Electrical Engineering, Stanford University

- M.S. Electrical Engineering, Stanford University

- Master of Engineering, Harvey Mudd College

- B.S. Engineering, Harvey Mudd College

Igor Carron

Igor has held several positions in business development and the management of technical teams in space and nuclear engineering projects. He is also the co-organizer of the Paris Machine Learning meetup, one of the largest Data Science meetups in the world with more than 7,000 members. Igor also writes a technical blog with a focus on algorithms, data and sensors that has been viewed more than 7 million times since its inception. Igor holds a Ph.D from Texas A&M University and an Engineering degree from INPG.

Luis Ceze

Luis Ceze is Co-founder and CEO at OctoML, Professor in the Paul G. Allen School of Computer Science and Engineering at the University of Washington, and Venture Partner at Madrona Venture Group. His research focuses on the intersection between computer architecture, programming languages, machine learning and biology. His current focus is on approximate computing for efficient machine learning andDNA-based data storage. He co-directs the Molecular Information Systems Lab (MISL), the Systems and Architectures for Machine Learning lab (SAMPL) and the Sampa Lab for HW/SW co-design. He is a recipient of an NSF CAREER Award, a Sloan Research Fellowship, a Microsoft Research Faculty Fellowship, the IEEE TCCA young Computer Architect Award and UIUC Distinguished Alumni Award.

Igor Arsovski

Igor Arsovski is the Chief Technical Officer in the ASIC Business Unit at Marvell.

He started with IBM Microelectronics in 2003 and has since worked at multiple companies across the full semiconductor vertical stack from Design Technology Co-Optimization(DTCO) of Memory & Standard Cells to full Architecture and PPA optimization of the highest performing Networking and Machine Learning ASICs.

He is currently responsible for Data Center and Automotive ASICs, defining IP, Methodology, and Packaging strategy for the next generation compute solutions.

His extended focus is energy efficient building blocks for Machine Learning, Modularity, 3D Memory Integration, and Artificial Intelligence Assistants for Chip Design.

Igor has authored more than 20 IEEE papers, has over 85 patents, and is serving on multiple conference committees.

Charles Macfarlane

Charles Macfarlane is CBO and Director at Codeplay Software in Edinburgh since 2014 responsible for sales, marketing and business development. Charles graduated from Glasgow University with an honours degree in Electronic Systems and Microprocessor Engineering. Charles then followed a career doing ASIC chip design in GEC Plessey Semiconductors and Pioneer, applications engineering and marketing with VLSI/Philips/NXP in South France, and product marketing director with Broadcom® in Cambridge for mobile multimedia solutions used by Nokia®, Samsung® and Raspberry Pi®.

Mike Henry

Jonathan Ross

Jonathan Ross is Groq’s technical founder and CEO. Prior to founding Groq he began what became Google’s TPU effort as a 20% project where he designed and implemented the core elements of the original chip. Jonathan next joined Google X’s Rapid Eval Team, the initial stage of the famed “Moonshots factory”, where he devised and incubated new Bets (Units) for Google’s parent company, Alphabet. Jonathan studied mathematics and computer science at NYU’s Courant Institute, and in his second year was the first Computer Science undergraduate to complete courses restricted to PhD students.

Satrajit Chatterjee

Sat is an Engineering Manager and Machine Learning Researcher at Google AI. His current research focuses on fundamental questions in deep learning (such as understanding why neural networks generalize at all) and on applications of ML to hardware design and verification (specifically hardware for ML acceleration).

Before Google, he was a Senior Vice President at Two Sigma, a leading quantitative investment manager, where he founded one of the first successful deep learning-based alpha research groups on Wall Street and led a team that built one of the earliest end-to-end FPGA-based trading systems for general purpose ultra-low latency trading. Prior to that, he was a Research Scientist at Intel where he worked on microarchitectural performance analysis and formal verification for on-chip networks.

He did his undergraduate studies at IIT Bombay, has a PhD in Computer Science from UC Berkeley, and has published in the top machine learning, design automation, and formal verification conferences.

Dr. Chris Eliasmith

Chris is a co-founder and co-CEO of ABR. Chris leads all of the scientific and technical aspects of ABR. Chris is also a professor at the University of Waterloo appointed in the Philosophy and Systems Design Engineering departments and cross-appointed to Computer Science. He holds the Canada Research Chair in Theoretical Neuroscience and is the director of the Centre for Theoretical Neuroscience (CTN) at the University of Waterloo. Chris has published over a hundred articles and two books: How to Build a Brain (Oxford University Press) and his seminal Neural Engineering. In 2015, he won the prestigious NSERC Polanyi Award for his research.

Anand Iyer

Arun Venkatachar

Buvna Ayyagari-Sangamalli

Buvna Ayyagari-Sangamalli heads the Design Technology team at Applied Materials. With a career in various roles from Design Engineering to development of Customer IP Subsystems, she is intimately familiar with design challenges. At Synopsys she played a pivotal role in growing the IP business, where she led the IP Applications Engineering team and launched Customer IP Subsystems for AI, Automotive, IoT and other segments. Prior to that, she played a critical role in defining low-power EDA design methodologies. At Intel she worked on various mobile, desktop and processor chips. Her well-rounded 20 years in the semiconductor industry straddled architecture, design, EDA and IP.

Craig Orr

Fadi Aboud

Fadi Aboud is a Sr. Principal Engineer at Intel Corporation. He leads the development and deployment of Tools, Flows and Methodology solutions for IP, SOC and Platform level power, performance and thermal. Fadi previously led the development and deployment of Intel’s custom design implementation flow, for the high-speed core IP design.

Fadi holds a degree in electrical engineering from the Technion Institute of Haifa-Israel, graduating in 1992. He currently lives in the city of Nazareth in Israel with his wife and three children.

Kim Hazelwood

Kim Hazelwood is an engineering leader whose expertise lies at the intersection of scalable computer systems and applied machine learning. Her roles at Facebook have included multiple engineering organizational leadership roles across Infrastructure and Research. Prior to Facebook, Kim held positions including Director of Research at Yahoo Labs, Software Engineer in the datacenter division of Google, Research Scientist at Intel, and tenured Associate Professor of Computer Science at the University of Virginia. Kim holds a PhD in Computer Science from Harvard University and has authored over 50 publications and one book. She is a recipient of the MIT "Top 35 Innovators under 35" award, the ACM SIGPLAN "Test of Time" Award, the Anita Borg Early Career Award, and an NSF Career Award. She currently serves on the Board of Directors for the Computing Research Association.

Paolo Faraboschi

Paolo Faraboschi leads research in the Systems Research Lab at HP Labs. His technical interests lie at the intersection of hardware and software and include low power servers and systems-on-a-chip, workload-optimized, highly-parallel and distributed systems, ILP and VLIW processor architectures, compilers, and embedded systems. Faraboschi’s current research focuses on next-generation data-centric systems. His work on system-level integration for low energy servers and scale-out architectures is a key element of the HP Moonshot System, HP’s new class of software-defined servers built to address the energy efficiency challenges of hyperscale datacenters.

Previously, Faraboschi led HP Labs research in system-level modeling and simulation, an effort that resulted in the COTSon open-source simulation platform. He is also the founder of HP’s Barcelona Research Office, which pioneered research in contentprocessing systems.. Before that, Faraboschi was technical lead for the Custom-Fit Processors Project at HP Labs, Cambridge (MA), building highly-optimized, softwaredefined CPU cores. In that role, he was the principal architect of the instruction set architecture for the Lx/ST200 family of VLIW embedded processor cores (developed with STMicroelectronics) which have been used for over a decade in a variety of audio, video, and imaging consumer products, including HP's printers and scanners.

A regular keynote speaker at conferences and industry events, Faraboschi is an IEEE Fellow for "contributions to embedded processor architecture & system-on-chip technology." An active member of the computer architecture community, he also serves regularly on IEEE program and organizational committees, was guest editor of the 2012 edition of IEEE Micro TopPicks, and is co-author (with Josh Fisher and Cliff Young) of the book, “Embedded Computing: a VLIW Approach to Architecture, Compilers and Tools.” A co-holder of 24 granted patents, several other patent applications, and co-author of over 65 scientific publications, Faraboschi received his M.S. and Ph.D. (Dottora)

Rick Stevens

Rick Stevens is Argonne’s Associate Laboratory Director for Computing, Environment and Life Sciences.

Stevens has been at Argonne since 1982, and has served as director of the Mathematics and Computer Science Division and also as Acting Associate Laboratory Director for Physical, Biological and Computing Sciences. He is currently leader of Argonne’s Exascale Computing Initiative, and a Professor of Computer Science at the University of Chicago Physical Sciences Collegiate Division. From 2000-2004, Stevens served as Director of the National Science Foundation’s TeraGrid Project and from 1997-2001 as Chief Architect for the National Computational Science Alliance.

Stevens is interested in the development of innovative tools and techniques that enable computational scientists to solve important large-scale problems effectively on advanced scientific computers. Specifically, his research focuses on three principal areas: advanced collaboration and visualization environments, high-performance computer architectures (including Grids) and computational problems in the life sciences. In addition to his research work, Stevens teaches courses on computer architecture, collaboration technology, virtual reality, parallel computing and computational science.

Tien Shiah

Tien Shiah is Senior Manager, Marketing for High Bandwidth Memory at Samsung Semiconductor Inc. In this capacity, he serves as the company’s product consultant, market expert, and evangelist for HBM in the Americas, focused on providing a clear understanding of the tremendous benefits offered by HBM in the enterprise and client marketplaces. He brings more than 16 years of product marketing experience from the semiconductor and storage industries, and has presented at a number of industry conferences, such as Flash Memory Summit, the Storage Developer Conference, and Dell EMC World. He holds an MBA from McGill University (Montreal, Canada), and an Electrical Engineering degree from the University of British Columbia.

Ziad Asghar

Ziad Asghar is Vice President, Product Management at Qualcomm Technologies, Inc (QTI). He leads Snapdragon roadmap planning and Application processor technologies, covering all QC product lines. Ziad drives the definition of the products ensuring that our products lead in technology and enable best in class user experiences while making tradeoffs between features, power, performance and cost. He also leads Application Processor technologies including Artificial Intelligence, Camera, Graphics, CPU, Audio, Video and Security. He also has responsibility for Competitive Analysis. Ziad works across all teams including engineering and product management to ensure that we have the leading roadmap in the industry and continue to set the standard on all application processor technologies. He works across all business units including Mobile, Automotive, Compute, XR, Edge Cloud and IoT.

He has more than 20 years of experience in the wireless semiconductor industry where he has held a broad set of leadership positions from R&D to product management. Prior to joining Qualcomm, Ziad was at Texas Instruments where he worked on systems design of UMTS & LTE and OMAP Product Management.

Ziad holds an MBA from UCSD and master’s degrees in electrical engineering from Purdue University and Southern Methodist University.

Amir Eyal

Robert Ober

Andrew Richards

CEO and co-founder of Codeplay, Andrew started his career writing video games in the days of 8-bit computers, progressing to become a lead games programmer at Eutechnyx™, where he wrote best-selling titles such as Pete Sampras Tennis and Total Drivin’. Codeplay have been producing compilers for games consoles, special-purpose processors and GPUs since then. As well as being CEO and Founder of Codeplay Software Ltd, Andrew is also the Chair of the Software working group of the HSA Foundation™ and former Chair of the SYCL™ for OpenCL™ sub-group of the Khronos® Group.

Kerrie Holley

Kerrie Holley joined United Health Group (UHG), Optum, as their first Technology Fellow and Senior Vice President focused on advancing and applying several technologies like artificial intelligence, deep learning, natural language processing, graph databases, IoT, genomics, and ambient computing.

Kerrie spent the bulk of his career at IBM where he was an IBM Fellow, Master Inventor and now IBM Fellow Emeritus. He was IBM’s first African American Distinguished Engineer. He is fond of appearing on ABC News and a TED talk to discuss IBM’s Watson the day after its historic debut on Jeopardy! Prior to Optum, Kerrie worked on maturing an analytics portfolio focused using machine learning and streaming analytics as a CTO with Cisco.

He holds a number of technology patents and is the author of two books: “Is Your Company Ready for Cloud” and “100 SOA Questions: Asked and Answered.” His third book is due to publish in 2021, “AI-First Healthcare” with co-author Dr. Siupo Becker, MD.

He received his Bachelor of Arts in Mathematics from DePaul University in Chicago; a Juris Doctor Degree and an honorary degree, Doctor of Humane Letters. See https://www.optum.com/business/about/data-analytics-technology/experts/kerrie-holley.html for more details.

Galina Grunin

I am a hands-on IT practitioner with expert knowledge and experience in deep learning, orchestration and pattern deployment, cloud computing architecture, software-defined storage, software-defined networking, adapting legacy systems for the cloud, web technologies, and application and middleware integration. My achievements in the above fields are recognized by over 40 U.S. patents in which I am a named inventor.

Prior to joining Optum, I was the lead architect/technical lead for various projects at IBM Cloud and IoT divisions. In those roles, I developed a cloud strategy and a reference architecture for cloud-based solutions; evaluated, enabled and optimized key third-party software and technology for potential partnership or acquisition; developed cognitive workloads for the new IoT edge platform; and assisted prospective and actual clients in evaluating and addressing cloud and IoT-related infrastructure, solutions and technologies.

Alex Karargyris

Kim Branson

Dr Kim Branson, is SVP and Global Head, AI/ML at GSK, based in San Francisco. Kim oversees a global team of more than 50 engineers and machine learning researchers. The GSK AI/ML team is focused on the application and development of AI methodology at the intersection of functional genomics and human genetics for target discovery, causal machine learning and clinical applications. Kim joined GSK in 2019 from Genentech where he was Head of AI, Early Clinical Development. Kim received his PhD in Computational Drug Design from University of Melbourne.

Kim has been involved in large-scale machine learning and medical informatics initiatives for more than 15 years, over a range of ventures from computational drug design to disease risk prediction. Kim received degrees from the University of Adelaide, and a PhD from the University of Melbourne (Australia). He was a Peter Doherty fellow and received postdoctoral training at Stanford University. He then held leadership and consulting roles in the pharmaceutical and medical informatics industry, notably at Vertex Pharmaceuticals.

Following this, Kim worked extensively in online search as a founding member of Discovery Engine (acquired by Twitter in 2009) and in health informatics as the Founding Chief Scientist of Gliimpse (acquired by Apple in 2017), and the Founding Chief Data Scientist at Lumiata, a predictive health analytics company.

Bronis de Supinski

Bronis R. de Supinski is the Chief Technology Officer (CTO) for Livermore Computing (LC) at Lawrence Livermore National Laboratory (LLNL). In this role, he is responsible for formulating LLNL's large-scale computing strategy and overseeing its implementation. His position requires frequent interaction with high performance computing (HPC) leaders and he oversees several collaborations with the HPC industry as well as academia. He is also the LLNL principal point of contact for the Scientific Discovery through Advanced Computing (SciDAC) program's Institute for Sustained Performance, Energy and Resilience (SUPER), for which he leads the resilience thrust.

Prior to becoming CTO for LC, Bronis led several research projects in LLNL's Center for Applied Scientific Computing (CASC). Most recently, he led the Exascale Computing Technologies (ExaCT) project and co-led the Advanced Simulation and Computing (ASC) program's Application Development Environment and Performance Team (ADEPT). ADEPT is responsible for the development environment, including compilers, tools and run time systems, on LLNL's large-scale systems. ExaCT explored several critical directions related to programming models, algorithms, performance, code correctness and resilience for future large scale systems. He currently continues his interests in these topics, particularly programming models, and serves as the Chair of the OpenMP Language Committee.

Bronis earned his Ph.D. in Computer Science from the University of Virginia in 1998, and he joined CASC in July 1998. His dissertation investigated shared memory coherence based on isotach logical time systems. His research has covered a wide range of topics, including applications of data mining techniques to performance analysis and modeling including performance modeling through non-linear regression techniques (i.e., artificial neural networks and piecewise polynomial regression), investigations into mechanisms and tools to improve memory performance, a variety of optimization techniques and tools for MPI, and several issues with OpenMP, including its memory model and tool support.

Throughout his career, Bronis has won several awards, including the prestigious Gordon Bell Prize in 2005 and 2006, as well as an R&D 100 for his leadership of a team that developed a novel scalable debugging tool. He serves on the program committees of numerous conferences and workshops. He is a member of the ACM and the IEEE Computer Society.

Zach DeVito

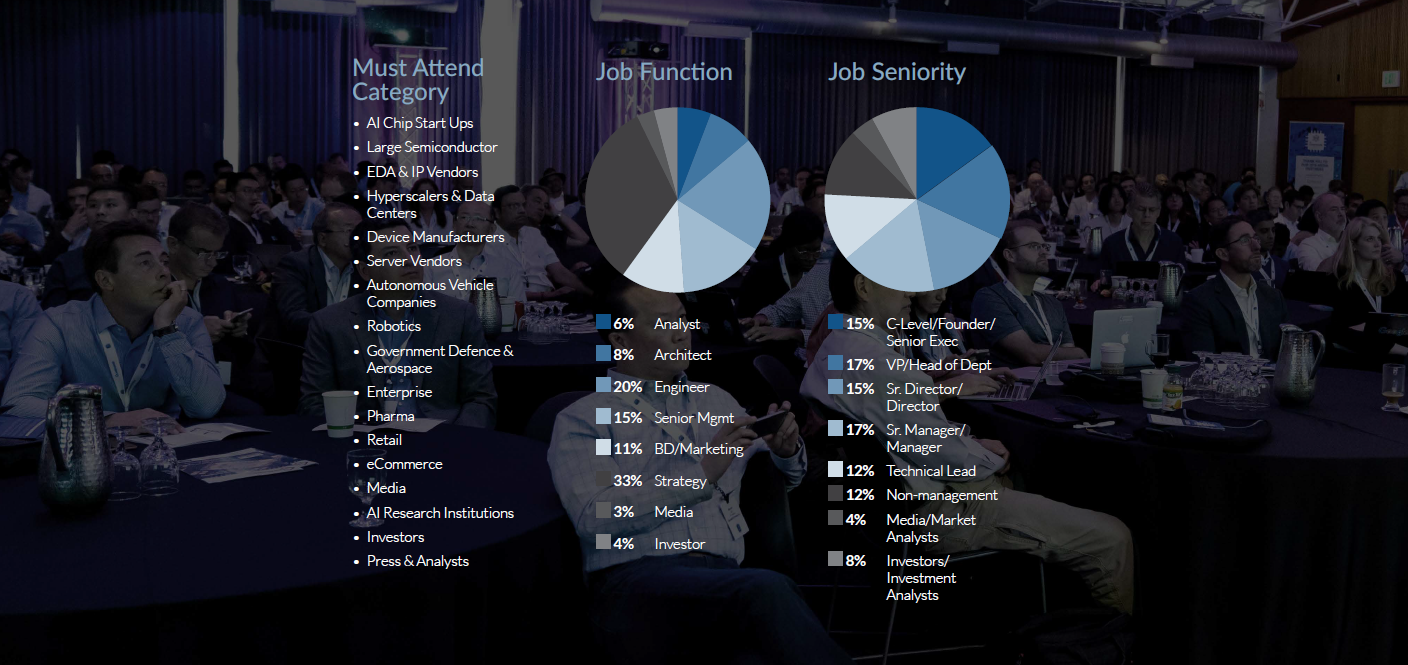

AUDIENCE BREAKDOWN

Past attendees include:

Platinum Partners

Gold Partners

Event Partners

Showcase Partner

Headline Media Partner

Media Partners

PARTNER WITH US

Based on your objectives, we can create bespoke packages designed specifically for you. Opportunities predominantly lie in 3 main categories: Thought Leadership, Branding, and Networking.

Interested in a media partnership?

We'd love to hear from you and how we can support one another to connect with the industry. Contact [email protected]

Interested in a media partner pass?

This year we have a very limited number of press passes available to attend the event. If you regularly cover the AI chip industry and want to stay at the cusp of innovation and hear the latest product and company launches, get in touch.

Contact: Finola McMahon, Marketing Director

fm@kisacoresearch.com

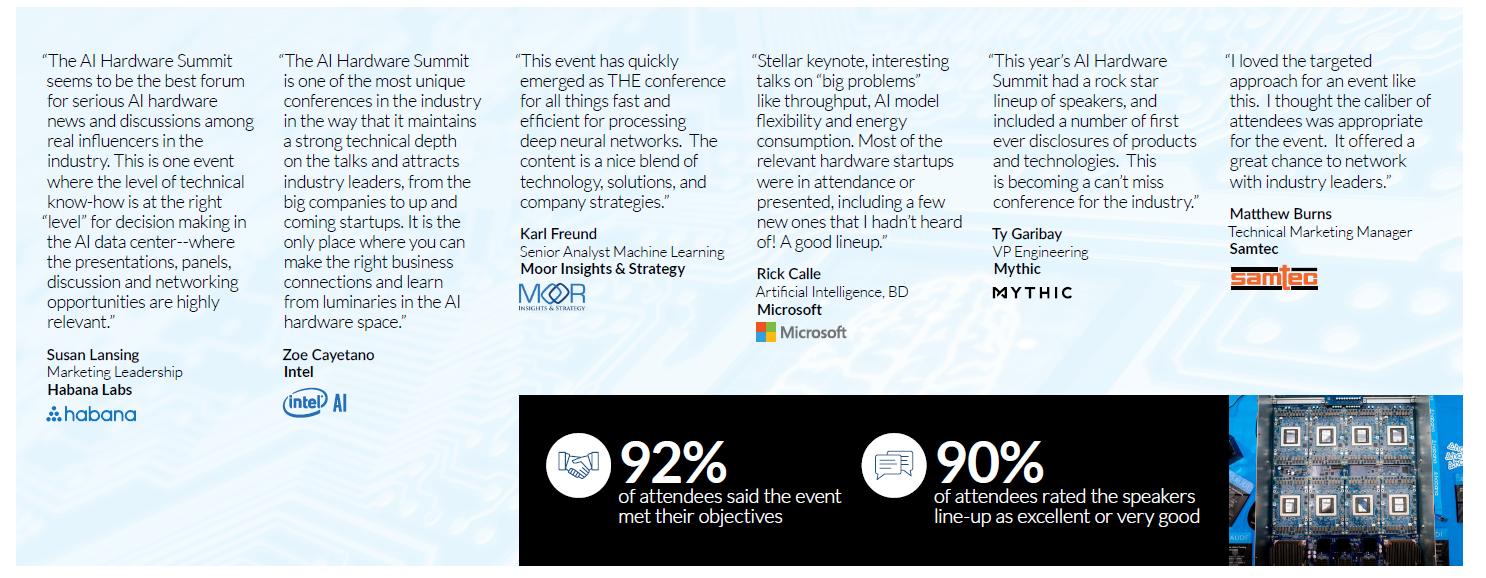

TESTIMONIALS

The Virtual Experience

Top 10 benefits

- Tailor Your Agenda

- More Audience Participation

- Improved Audience Visibility

- On-Demand Content

- High Quality Speakers

- More Networking Opportunities

- Save Time & Money

- Increased Content

- More insights

- Business Development Opportunities - Talk to our team to find out out more [email protected].

The Agenda

Please complete your details to receive a copy of the 2020 agenda to explore the type of topics that will be covered.

Watch video highligts from the AI Hardware Summit 2019:

Download 2020 Virtual Agenda

About Kisaco Research

Kisaco Research produces, designs and hosts B2B industry conferences, exhibitions and communities – focused on a specialized selection of topic areas.

Meet industry peers that will help build a career-changing network for life.

Learn from the mistakes of your peers as much as their successes—ambitious industry stalwarts who are happy to share not just what has made them successful so far but also their plans for future proofing their companies.

Note down the inspired insight that will form the foundation for future strategies and roadmaps, both at our events and through our online communities.

Invest both in your company growth and your own personal development by signing up to one of our events and get started.